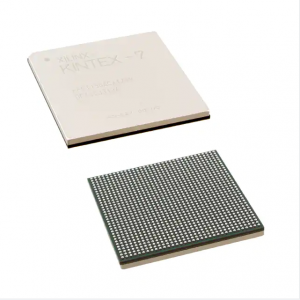

Xilinx/XC7K480T-2FFG1156I/XC7K480T/IC BOM FPGA/circuíto integrado

Especificacións

| Atributo do produto | Valor do atributo |

| Fabricante: | Xilinx |

| Categoría do produto: | FPGA - Field Programmable Gate Array |

| RoHS: | Detalles |

| Serie: | XC7K480T |

| Número de elementos lóxicos: | 477760 LE |

| Número de E/S: | 400 E/S |

| Tensión de alimentación - Min: | 1 V |

| Tensión de alimentación - Max: | 1 V |

| Temperatura mínima de funcionamento: | - 40 C |

| Temperatura máxima de funcionamento: | + 100 C |

| Taxa de datos: | 12,5 Gb/s |

| Número de transceptores: | 32 Transceptor |

| Estilo de montaxe: | SMD/SMT |

| Paquete/Estuche: | FCBGA-1156 |

| Marca: | Xilinx |

| RAM distribuída: | 6788 kbit |

| Bloque RAM incorporado - EBR: | 34380 kbit |

| Frecuencia de operación máxima: | 640 MHz |

| Sensible á humidade: | Si |

| Número de bloques de matriz lóxica - LAB: | 37325 LABORATORIO |

| Tensión de alimentación de funcionamento: | 1 V |

| Tipo de produto: | FPGA - Field Programmable Gate Array |

| Cantidade do paquete de fábrica: | 1 |

| Subcategoría: | CI lóxicos programables |

| Nome comercial: | Kintex |

XC7K480T-2FFG1156I Descrición xeral dos FPGA

Descrición xeral

Os FPGA da serie Xilinx® 7 comprenden catro familias de FPGA que abordan a gama completa de requisitos do sistema, que van desde aplicacións de baixo custo, factor de forma pequeno, sensibles aos custos e de gran volume ata ancho de banda de conectividade de gama alta, capacidade lóxica e capacidade de procesamento de sinal. para as aplicacións de alto rendemento máis esixentes.Os FPGA da serie 7 inclúen:

• Familia Spartan®-7: optimizada para baixo custo, menor potencia e alto rendemento de E/S.Dispoñible en envases de baixo custo e de factor de forma moi pequeno para a menor pegada de PCB.

• Familia Artix®-7: optimizada para aplicacións de baixa potencia que requiren transceptores en serie e alto rendemento lóxico e DSP.Ofrece o menor custo total da factura de materiais para aplicacións de alto rendemento e sensibles aos custos.

• Familia Kintex®-7: optimizada para obter o mellor prezo-rendemento cunha mellora 2X en comparación coa xeración anterior, o que permite unha nova clase de FPGA.

• Familia Virtex®-7: optimizada para o maior rendemento e capacidade do sistema cunha mellora do rendemento do sistema.Dispositivos de maior capacidade habilitados pola tecnoloxía de interconexión de silicio apilado (SSI).

Construídos sobre unha tecnoloxía de proceso de última xeración, alto rendemento e baixa potencia (HPL), 28 nm, high-k metal gate (HKMG), os FPGA da serie 7 permiten un aumento incomparable no rendemento do sistema con 2,9 Tb/ s de ancho de banda de E/S, 2 millóns de capacidade de células lóxicas e 5,3 TMAC/s DSP, mentres consumen un 50 % menos de enerxía que os dispositivos da xeración anterior para ofrecer unha alternativa totalmente programable aos ASSP e ASIC.

características

• Lóxica FPGA avanzada de alto rendemento baseada na tecnoloxía de táboa de busca de 6 entradas (LUT) real configurable como memoria distribuída.

• 36 Kb de RAM de bloque de dobre porto con lóxica FIFO integrada para almacenamento de datos no chip.

• Tecnoloxía SelectIO™ de alto rendemento con compatibilidade con interfaces DDR3 de ata 1.866 Mb/s.

• Conectividade en serie de alta velocidade con transceptores multigigabit integrados desde 600 Mb/s ata velocidades máximas de 6,6 Gb/s ata 28,05 Gb/s, que ofrecen un modo especial de baixa potencia, optimizado para interfaces chip a chip .

• Unha interface analóxica configurable polo usuario (XADC), que incorpora conversores analóxico-dixital dobre de 12 bits 1MSPS con sensores térmicos e de subministración no chip.

• Cortes DSP con multiplicador de 25 x 18, acumulador de 48 bits e sumador previo para un filtrado de alto rendemento, incluído o filtrado de coeficiente simétrico optimizado.

• Poderosas tellas de xestión de reloxos (CMT), que combinan bloques de bucle de bloqueo de fase (PLL) e xestor de reloxo de modo mixto (MMCM) para unha alta precisión e unha baixa fluctuación.

• Bloque integrado para PCI Express® (PCIe), para deseños de ata x8 Gen3 Endpoint e Root Port.

• Ampla variedade de opcións de configuración, incluíndo soporte para memorias de mercadorías, cifrado AES de 256 bits con autenticación HMAC/SHA-256 e detección e corrección SEU integradas.

• Embalaxe de chip flip-chip de baixo custo, conexión por cable, sen tapa e alta integridade do sinal que ofrece unha migración sinxela entre os membros da familia no mesmo paquete.Todos os paquetes dispoñibles sen Pb e paquetes seleccionados en opción Pb.

• Deseñado para un alto rendemento e unha potencia máis baixa con 28 nm, proceso HKMG, HPL, tecnoloxía de proceso de tensión de núcleo de 1,0 V e opción de tensión de núcleo de 0,9 V para unha potencia aínda máis baixa.

A serie XC7K480T-2FFG1156I de FPGA (Field Programable Gate Array) de Xilinx é FPGA, Kintex-7, MMCM, PLL, 400 E/S, 710 MHz, 477760 células, 970 mV a 1,03 V e substitutos FCBGA, Vista-1 V, FCBGA, alternativas con follas de datos, stock, prezos dos distribuidores autorizados en FPGAkey.com e tamén pode buscar outros produtos FPGA.

características

Lóxica FPGA avanzada de alto rendemento baseada na tecnoloxía de táboa de busca de 6 entradas (LUT) real configurable como memoria distribuída.

RAM de bloque de 36 Kb de dobre porto con lóxica FIFO integrada para almacenamento en búfer de datos no chip.

Tecnoloxía SelectIO de alto rendemento con compatibilidade con interfaces DDR3 de ata 1.866 Mb/s.

Conectividade en serie de alta velocidade con transceptores multigigabit integrados desde 600 Mb/s ata velocidades máximas de 6,6 Gb/s ata 28,05 Gb/s, que ofrece un modo especial de baixa potencia, optimizado para interfaces chip a chip.

Unha interface analóxica configurable polo usuario (XADC), que incorpora conversores analóxico-dixital 1MSPS duales de 12 bits con sensores térmicos e de subministración no chip.

Cortes DSP con multiplicador de 25 x 18, acumulador de 48 bits e sumador previo para un filtrado de alto rendemento, incluído o filtrado de coeficiente simétrico optimizado.

Potentes mosaicos de xestión de reloxos (CMT), que combinan bloques de bucle de bloqueo de fase (PLL) e xestor de reloxo de modo mixto (MMCM) para unha alta precisión e unha baixa fluctuación.

Bloque integrado para PCI Express (PCIe), para deseños de ata x8 Gen3 Endpoint e Root Port.

Ampla variedade de opcións de configuración, incluíndo soporte para memorias de produtos básicos, cifrado AES de 256 bits con autenticación HMAC/SHA-256 e detección e corrección SEU integradas.

Embalaxe de chip flip-chip de baixo custo, conexión por cable, sen tapa e alta integridade do sinal que ofrece unha migración sinxela entre os membros da familia no mesmo paquete.Todos os paquetes dispoñibles sen Pb e paquetes seleccionados en opción Pb.

Deseñado para un alto rendemento e unha potencia máis baixa con 28 nm, HKMG, proceso HPL, tecnoloxía de proceso de tensión de núcleo de 1,0 V e opción de tensión de núcleo de 0,9 V para unha potencia aínda máis baixa.