SN74ACT244PWR Búfers de 8 canles de 4,5 V a 5,5 V con entradas CMOS compatibles con TTL e saídas de 3 estados

Atributos do produto

| RoHS da UE | Conforme |

| ECCN (EUA) | EAR99 |

| Estado da peza | Activo |

| HTS | 8542.39.00.01 |

| Automoción | No |

| PPAP | No |

| Familia lóxica | ACT |

| Función lóxica | Controlador de búfer/línea |

| Número de elementos por chip | 2 |

| Número de canles por chip | 8 |

| Número de entradas por chip | 8 |

| Número de activacións de entrada por chip | 0 |

| Número de saídas por chip | 8 |

| Número de activacións de saída por chip | 2 Baixo |

| Parada de autobuses | No |

| Polaridade | Non inverter |

| Tempo de retardo de propagación máximo @ CL máximo (ns) | 9@4.5V to 5.5V |

| Tempo de atraso de propagación absoluto (ns) | 10.5 |

| Tecnoloxía de Procesos | CMOS |

| Tipo de sinal de entrada | Single-Ended |

| Tipo de saída | 3-Estado |

| Máxima corrente de saída de baixo nivel (mA) | 24 |

| Corriente de saída máxima de alto nivel (mA) | -24 |

| Tensión de alimentación de funcionamento mínima (V) | 4.5 |

| Tensión de alimentación de funcionamento típica (V) | 5 |

| Tensión de alimentación de funcionamento máxima (V) | 5.5 |

| E/S tolerantes (V) | 5.5 Entradas |

| Corriente de reposo máxima (uA) | 4 |

| Condición de proba de retardo de propagación (pF) | 50 |

| Temperatura mínima de funcionamento (°C) | -40 |

| Temperatura máxima de funcionamento (°C) | 85 |

| Grao de temperatura do provedor | Comercial |

| Embalaxe | Cinta e carrete |

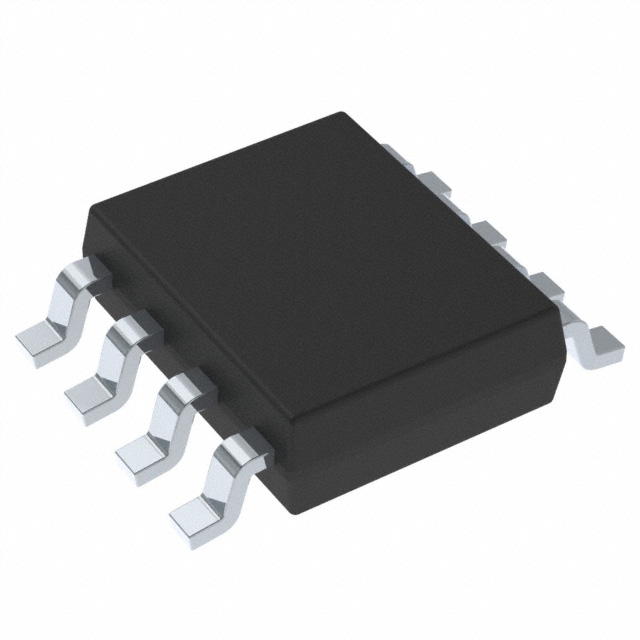

| Montaxe | Montaxe en superficie |

| Altura do paquete | 1,05 (máx.) |

| Ancho do paquete | 4,5 (máx.) |

| Lonxitude do paquete | 6,6 (máx.) |

| PCB cambiou | 20 |

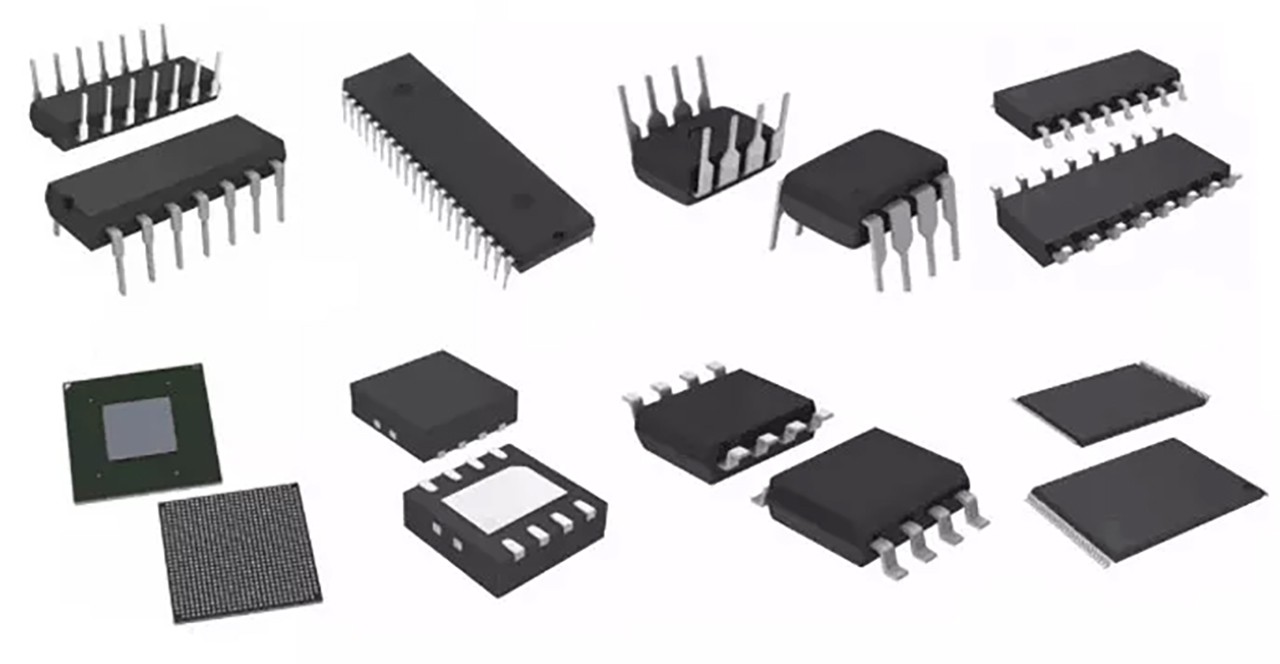

| Nome do paquete estándar | SOP |

| Paquete de provedores | TSSOP |

| Contador de pins | 20 |

| Forma de chumbo | Á de gaivota |

Introdución detallada

Estes búfers e controladores octais SNx4ACT244 están deseñados especificamente para mellorar o rendemento e a densidade dos controladores de enderezos de memoria de 3 estados, controladores de reloxo e receptores e transmisores orientados ao bus.Os dispositivos SNx4ACT244 están organizados como dous búfers e controladores de 4 bits con entradas de saída (OE) separadas.Cando OE é baixo, o dispositivo pasa datos non invertidos das entradas A ás saídas Y.Cando OE é alto, as saídas están no estado de alta impedancia.

Escribe aquí a túa mensaxe e envíanolo