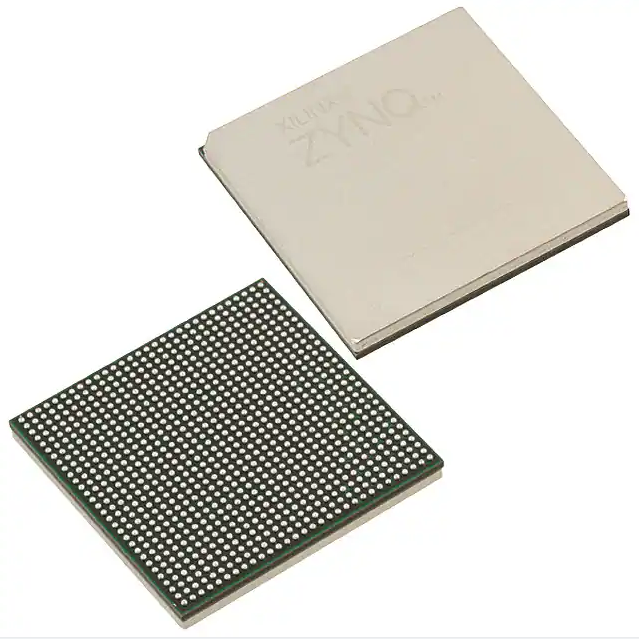

Circuíto integrado XC5VFX30T-2FFG665I novo e orixinal

Atributos do produto

| TIPO | DESCRICIÓN | SELECCIONAR |

| Categoría | Circuítos integrados (CI) |

|

| Mfr | AMD Xilinx |

|

| Serie | Virtex®-5 FXT |

|

| Paquete | Bandexa |

|

| Estado do produto | Activo |

|

| Número de LAB/CLB | 2560 |

|

| Número de elementos lóxicos/células | 32768 |

|

| Total de bits de RAM | 2506752 |

|

| Número de E/S | 360 |

|

| Tensión - Alimentación | 0,95 V ~ 1,05 V |

|

| Tipo de montaxe | Montaxe en superficie |

|

| Temperatura de operación | -40 °C ~ 100 °C (TJ) |

|

| Paquete / Estuche | 665-BBGA, FCBGA |

|

| Paquete de dispositivos do provedor | 665-FCBGA (27×27) |

|

| Número de produto base | XC5VFX30 |

|

Informar dun erro de información do produto

Ver Similar

Documentos e medios

| TIPO DE RECURSOS | ENLACE |

| Fichas técnicas | Virtex-5 Visión xeral da familia |

| Información Ambiental | Xilinx REACH211 Cert |

| Deseño/especificación de PCN | Aviso de envío cruzado sen chumbo 31/out/2016 Variación de material de desenvolvemento múltiple 16/12/2019 |

Clasificacións ambientais e de exportación

| ATRIBUTO | DESCRICIÓN |

| Estado RoHS | Conforme ROHS3 |

| Nivel de sensibilidade á humidade (MSL) | 4 (72 horas) |

| Estado REACH | REACH non afectado |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Array de porta programable en campo

Amatriz de porta programable en campo(FPGA) é uncircuíto integradodeseñado para ser configurado por un cliente ou un deseñador despois da fabricación, de aí o termoprogramable en campo.A configuración FPGA especifícase xeralmente mediante alinguaxe de descrición do hardware(HDL), similar ao usado para uncircuíto integrado específico da aplicación(ASIC).Diagramas de circuítosforon usados anteriormente para especificar a configuración, pero isto é cada vez máis raro debido á aparición deautomatización de deseño electrónicoferramentas.

As FPGA conteñen unha matriz deprogramable bloques lóxicos, e unha xerarquía de interconexións reconfigurables que permiten conectar bloques entre si.Os bloques lóxicos poden ser configurados para realizar complexosfuncións combinatorias, ou actuar como sinxeloportas lóxicascomoEeXOR.Na maioría dos FPGA, os bloques lóxicos tamén inclúenelementos de memoria, que pode ser sinxeloSandaliasou bloques de memoria máis completos.[1]Moitos FPGA pódense reprogramar para implementar diferentesfuncións lóxicas, permitindo flexibleinformática reconfigurablecomo se realiza ensoftware informático.

As FPGA teñen un papel notablesistema integradodesenvolvemento debido á súa capacidade para iniciar o desenvolvemento de software do sistema simultaneamente co hardware, permitir simulacións de rendemento do sistema nunha fase moi inicial do desenvolvemento e permitir varias probas do sistema e iteracións de deseño antes de finalizar a arquitectura do sistema.[2]

Historia[editar]

A industria FPGA xurdiumemoria programable de só lectura(PROM) edispositivos lóxicos programables(PLD).Tanto os PROM como os PLD tiñan a opción de ser programados por lotes nunha fábrica ou no campo (programables en campo).[3]

Alterafoi fundada en 1983 e entregou o primeiro dispositivo lóxico reprogramable da industria en 1984, o EP300, que presentaba unha ventá de cuarzo no paquete que permitía aos usuarios facer brillar unha lámpada ultravioleta na matriz para borrar oEPROMcelas que tiñan a configuración do dispositivo.[4]

Xilinxproduciu o primeiro programable de campo comercialmente viablematriz de portasen 1985[3]- o XC2064.[5]O XC2064 tiña portas programables e interconexións programables entre portas, o inicio dunha nova tecnoloxía e mercado.[6]O XC2064 tiña 64 bloques lóxicos configurables (CLB), con dúas entradas de trestáboas de busca(LUT).[7]

En 1987, oCentro de Guerra de Superficie Navalfinanciou un experimento proposto por Steve Casselman para desenvolver unha computadora que implementase 600.000 portas reprogramables.Casselman tivo éxito e en 1992 emitiuse unha patente relacionada co sistema.[3]

Altera e Xilinx continuaron sen desafíos e creceron rapidamente desde 1985 ata mediados da década de 1990, cando xurdiron os competidores, erosionando unha parte importante da súa cota de mercado.En 1993, Actel (agoraMicrosemi) atendeu ao 18 por cento do mercado.[6]

A década de 1990 foi un período de rápido crecemento das FPGA, tanto na sofisticación dos circuítos como no volume de produción.A principios da década de 1990, os FPGA usáronse principalmentetelecomunicaciónsetraballo en rede.A finais da década, as FPGA atoparon o seu camiño en aplicacións de consumo, automoción e industriais.[8]

En 2013, Altera (31 por cento), Actel (10 por cento) e Xilinx (36 por cento) representaban xuntos aproximadamente o 77 por cento do mercado de FPGA.[9]

Empresas como Microsoft comezaron a usar FPGA para acelerar sistemas de alto rendemento e computacionalmente intensivos (como ocentros de datosque operan os seusBuscador Bing), debido árendemento por vatiovantaxes que ofrecen os FPGA.[10]Microsoft comezou a usar FPGA paraacelerarBing en 2014 e en 2018 comezou a implantar FPGA noutras cargas de traballo do centro de datos para as súasAzure Computación na nubeplataforma.[11]

As seguintes liñas de tempo indican o progreso en diferentes aspectos do deseño de FPGA:

Portas

- 1987: 9.000 portas, Xilinx[6]

- 1992: 600.000, Departamento de Guerra de Superficie Naval[3]

- Principios dos 2000: millóns[8]

- 2013: 50 millóns, Xilinx[12]

Tamaño do mercado

- 1985: Primeira FPGA comercial: Xilinx XC2064[5][6]

- 1987: 14 millóns de dólares[6]

- c.1993: > 385 millóns de dólares[6][verificación fallida]

- 2005: 1.900 millóns de dólares[13]

- Estimacións de 2010: 2.750 millóns de dólares[13]

- 2013: 5.400 millóns de dólares[14]

- Estimación para 2020: 9,8 millóns de dólares[14]

O deseño comeza

Ainicio do deseñoé un novo deseño personalizado para a súa implementación nunha FPGA.

Deseño[editar]

As FPGA contemporáneas teñen grandes recursos deportas lóxicase bloques de RAM para implementar cálculos dixitais complexos.Como os deseños FPGA empregan taxas de E/S moi rápidas e datos bidireccionaisautobuses, convértese nun reto verificar o momento correcto dos datos válidos dentro do tempo de configuración e tempo de espera.

Planificación de pisospermite a asignación de recursos dentro das FPGA para cumprir estes límites de tempo.Os FPGA pódense usar para implementar calquera función lóxica que sexaASICpode realizar.A capacidade de actualizar a funcionalidade despois do envío,reconfiguración parcialdunha parte do deseño[17]e os baixos custos de enxeñería non recorrentes relativos a un deseño ASIC (a pesar do custo unitario xeralmente máis elevado), ofrecen vantaxes para moitas aplicacións.[1]

Algunhas FPGA teñen características analóxicas ademais de funcións dixitais.A característica analóxica máis común é un programabletaxa de descensoen cada pin de saída, permitindo que o enxeñeiro estableza taxas baixas en pinos con carga leve que doutro xeitoanelouparellainaceptablemente, e establecer taxas máis altas en pinos moi cargados en canles de alta velocidade que doutro xeito correrían demasiado lentamente.[18][19]Tamén son comúns o cuarzoosciladores de cristal, osciladores de resistencia-capacitancia no chip ebucles bloqueados en fasecon incorporadoosciladores controlados por voltaxeutilízase para a xeración e xestión de reloxos, así como para os reloxos de transmisión do serializador-deserializador de alta velocidade (SERDES) e a recuperación do reloxo do receptor.Son bastante comúns os diferenciaiscomparadoresnos pinos de entrada deseñados para conectarsesinalización diferencialcanles.Uns poucos "sinal mixtoAs FPGA” teñen periféricos integradosconversores analóxico a dixital(ADC) econversores de dixital a analóxico(DAC) con bloques de acondicionamento de sinal analóxico que lles permiten funcionar como asistema nun chip(SoC).[20]Estes dispositivos difuminan a liña entre unha FPGA, que leva uns e ceros dixitais no seu tecido de interconexión programable interna, ematriz analóxica programable en campo(FPAA), que transporta valores analóxicos no seu tecido de interconexión programable interna.